Cyclical demand and risks to Asia-based supply chains require more resilience than ever from US semiconductor manufacturers. Many companies see investing in domestic production capacity as the solution, and recent government incentives reinforce this view. But adding capacity through capital expenditures (capex) is costly and slow and restricts flexibility when demand changes. What’s more, higher capital intensity hurts stock market performance.

Chip makers should consider a different strategy. Rather than relying on capex, they can expand the capacity of their fabrication plants by improving productivity. This approach helps companies swiftly respond to demand fluctuations, reduces the risk of overinvestment, and enhances financial returns.

For companies that invest in productivity, the improvement opportunities are substantial. A BCG benchmarking study found significant productivity gaps in tool uptime, standby time, and speed. By identifying bottlenecks, setting ambitious performance goals, and evaluating improvement levers, chip makers can boost fab productivity without using capex. And with the help of

advanced digital tools

, chip makers can create innovative solutions to tackle chronic or systemic productivity losses.

The Case for Expansion Without Capital Expenditures

Semiconductor manufacturers are no strangers to uncertainty and the need for resilience . For decades, cyclical demand has featured persistently across their business landscape. The recent environment has been especially challenging, with the pandemic causing a severe chip shortage, followed by a sharp drop in demand. At the same time, the concentration of production capacity in Asia has made chip makers vulnerable to geopolitical risks and supply chain disruptions.

To enhance the stability of their production networks, US-based manufacturers are ramping up capacity in North America. Indeed, the federal government (through the CHIPS Act of 2022) and local governments have provided incentives that encourage semiconductor companies to invest capital to build or expand fabs domestically.

Using capex to expand capacity, however, has important drawbacks.

Investments—building a leading-edge fabrication plant, for example—are growing more expensive and time-consuming as process nodes become smaller and critical equipment supply tightens. As a result, this approach does not help manufacturers ramp up and scale down capacity quickly.

Considering the downside, we believe that semiconductor manufacturers should prioritize capex-free expansion to build their resilience. That will enable companies to quickly ramp up capacity when demand rises. Conversely, when demand declines, no investment is lost. In our experience, while investors recognize the capital-intensive nature of semiconductor manufacturing, they are typically wary of companies with high capital intensity, and they reward companies that demonstrate efficient capital deployment.

Productivity improvement is a crucial aspect of capex-free capacity expansion. Our research indicates that many semiconductor manufacturers are operating below optimal production levels, leading to decreased wafer output and margin erosion. Companies should maximize productivity improvements before pursuing other avenues for capex-free expansion, such as outsourcing and production as a service , or relying on alternative sources of capital, such as government funding or customer investments.

Productivity Gaps Point to Improvement Opportunities

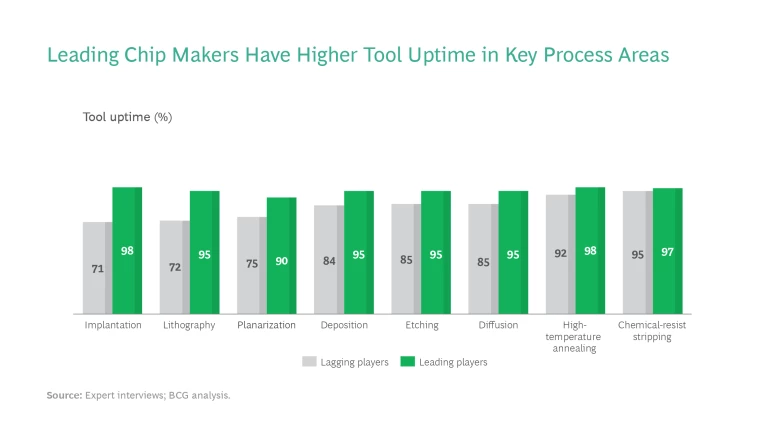

A recent BCG benchmarking study of fab performance found wide productivity gaps between leading and lagging players, indicating that laggards have significant room for improvement. The benchmarking focused on tool uptime, standby time, and speed.

Uptime. In many process areas, the tool uptime of leading companies exceeds that of laggards by 10% or more. (See the exhibit.) For lithography, often considered the most critical process area, the gap exceeds 20% for mature process nodes in a 300-millimeter fab. The size of the gaps suggests that laggards could increase their annual output by tens of thousands of wafers. Lost uptime results from various factors, such as issues with maintenance scheduling, spare parts inventory management, and a lack of standardization in maintenance procedures.

Standby Time. Chip makers often have inefficient fab scheduling and dispatching policies, leading to decreased tool utilization. Although policies are meant to minimize standby time while meeting quality standards, overly complicated rules and restrictions often increase standby time and hurt utilization. Our benchmarking study found that a suboptimal chamber configuration and run mode reduced the utilization of an etch-tool group by 5%, resulting in an annual capacity loss of more than 50,000 semiconductor wafers. However, opportunities to reduce standby time are not obvious and typically require complicated changes in fab policies. Leading players have started experimenting with digital applications and advanced analytical tools to address these challenges.

Speed. Many semiconductor companies focus on developing process recipes to maximize yield. But they often overlook optimizing tool speed, which leads to longer cycle time and decreased throughput. Outdated software and redundant process steps also hinder tool speed. Improving tool speed requires cross-functional collaboration to thoroughly examine the root causes of impediments. Our benchmarking study found an annual capacity loss of more than 10,000 wafers in cases where the setup was suboptimized for a deposition tool group (used to create insulating and conducting materials to build a semiconductor device).

A Four-Step Approach to Boost Productivity

Semiconductor manufacturers can use a four-step approach to cut productivity losses and improve overall fab productivity.

1. Identify the main tools that cause bottlenecks. Focus on tools that are used most and that limit fab output for long periods. Include tools that might limit fab output temporarily because of one-off events, such as changes to the mix of products.

2. Define your performance North Star. Set aspirational targets for performance improvements. For underperforming fabs, internal benchmarking against the company’s other plants provides a clear view of the potential opportunities and the best practices for capturing them. For the best-performing fabs, use external benchmarking to compare performance with that of competitors and derive improvement targets.

3. Identify levers for improvement using in-depth assessments. Analyze data on the historical performance of bottleneck tools to identify the major causes of tool downtime and idle time. Use issue trees to thoroughly identify ways to improve tool uptime, standby time, and speed. There are many improvement levers to consider, including:

- Scheduling preventive maintenance based on usage rather than the calendar.

- Reducing maintenance time by improving maintenance procedures and increasing the availability of spare parts.

- Reconsidering policies that inhibit certain practices and removing unnecessary constraints in order to improve tool utilization.

- Eliminating unneeded quality control checks that impede tool utilization.

- Regularly examining existing process recipes to eliminate redundant steps and optimize the setup to improve tool speed.

After identifying key improvement levers, collaborate with the shop-floor team to create specific initiatives to meet performance goals. For some bottlenecks, such as a low-cost furnace, the potential improvement may be small. In such cases, consider making incremental capex investments to remove nonstructural constraints and stabilize operations.

4. Set up governance and tracking mechanisms. Establish a governance structure to review progress and guide the improvement program. The fab leadership team and process area managers should meet regularly to evaluate the status of milestones, address roadblocks, and share insights. Moreover, leaders of the fab and corporate functions, such as finance and strategy, should convene at regular intervals. Such steering committees can conduct a high-level progress review, showcase major achievements, and offer strategic guidance. Both types of meetings should be facilitated by the manufacturing function.

Track improvements using KPIs such as uptime, downtime, utilization, and daily movements of wafers through the fab. Utilize digital program management tools to monitor progress toward milestones and financial impact.

Enhance the program’s success by encouraging open communication between management and employees. For instance, distribute a monthly or quarterly newsletter to highlight changes and accomplishments. And survey employees regularly to provide insight into employee sentiment and gather anonymous feedback.

Be sure to repeat and regularly review any improvement program. Shifts in demand, changes to the tool portfolio, and process technology upgrades may affect which tools are bottlenecks. Adapt North Star aspirations based on evolving business needs and leadership goals.

Use Advanced Digital Tools to Address Chronic or Systemic Issues

The four-step approach can tackle many common sources of productivity loss. But to address chronic or systemic losses, chip makers must be creative. Leading manufacturers are using cutting-edge digital tools, developed in-house or by third parties, to define innovative solutions. Although this is still an emerging field, early adopters have seen benefits.

For example, a top semiconductor manufacturer applied predictive maintenance to its auxiliary equipment (such as cooling water pumps) to reduce the frequency and cost of servicing. It also utilized an advanced scheduling system, powered by machine learning, to identify which time window for preventive maintenance would disrupt production least.

In our case experience, we have seen several digital applications used to boost fab productivity. These include:

- A digital twin that simulates manufacturing parameters in order to fine-tune them and maximize throughput.

- A digital tool that integrates data from multiple sources to automatically plan fab production. The tool allows companies to remove scheduling constraints across manufacturing stages (for example, lot dispatch or release) and thereby determine production sequences that maximize productivity. One US-based semiconductor manufacturer improved profits from its existing asset base by more than $20 million after implementing this tool.

- A digital control tower that accelerates and optimizes the process of sales and operations planning. It provides visibility into KPIs across the value chain, determines supply chain risks, and takes proactive steps to alleviate bottlenecks.

US semiconductor manufacturers may be tempted to invest capex to build or expand domestic production capacity. But prioritizing capex-free expansion through productivity improvements is a better strategy in many situations. This approach enables chip makers to enhance their resilience without increasing their capital intensity. Innovative digital tools are aiding efforts to tackle the toughest process bottlenecks. Companies that succeed will reap the benefits of superior operational and financial performance.